05/25일(월) 230차 판매 마감!

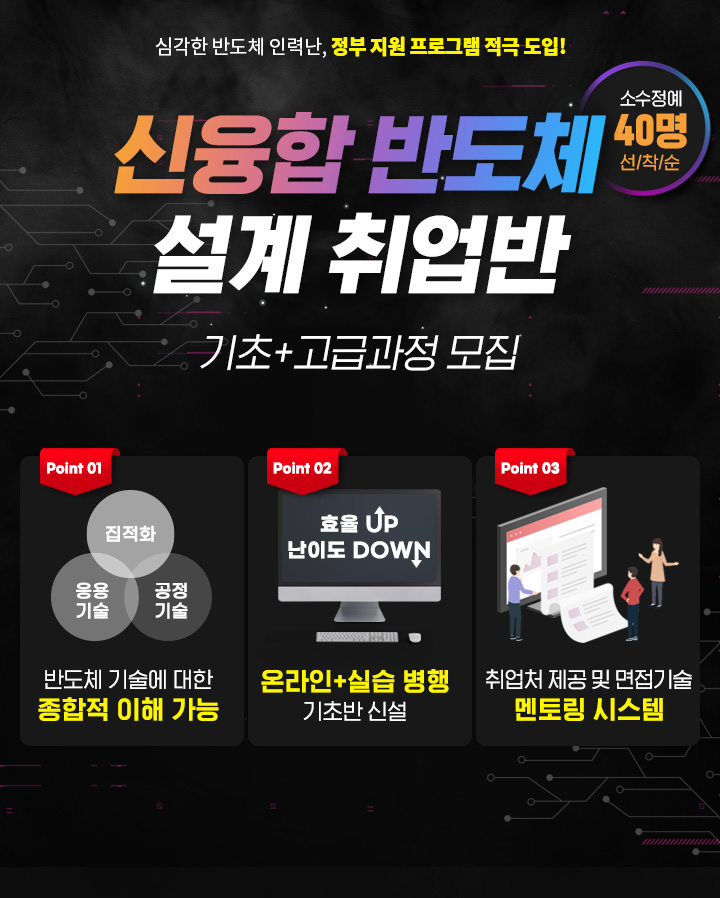

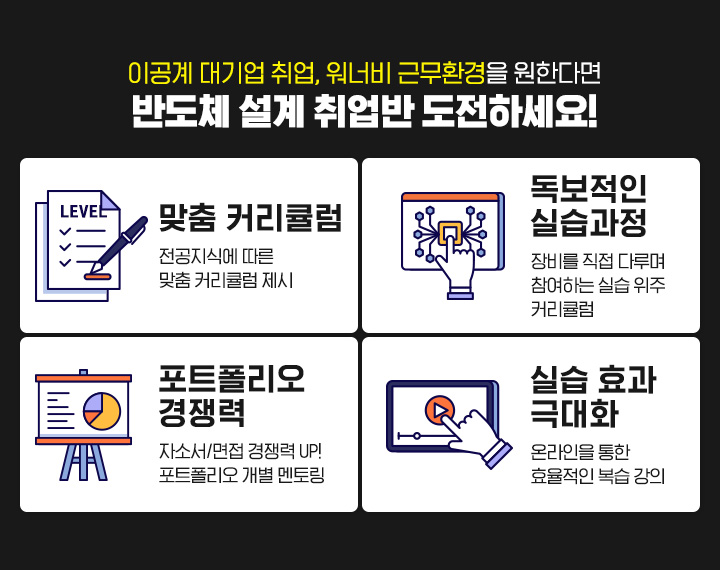

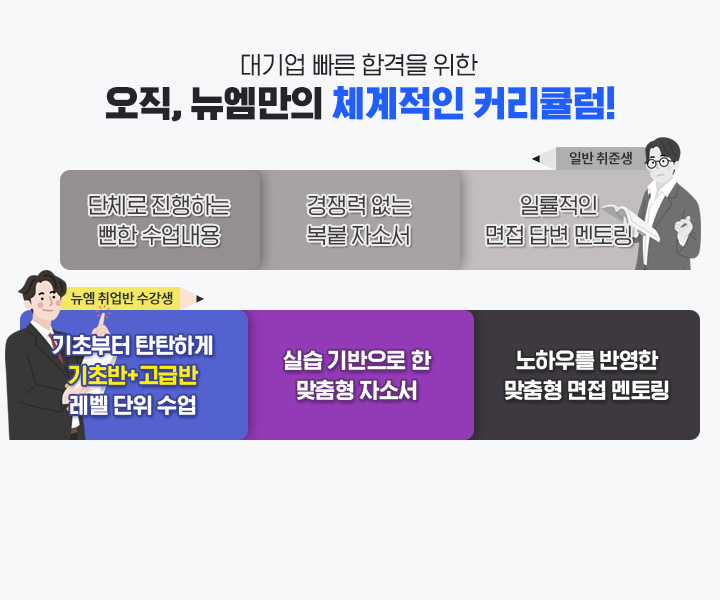

1. 신입생 모집요강

본교육원은 수업 및 자격증 취득을 통해 교육부장관 명의의 '전문학사' 및 '학사학위' 취득이 가능하며 학점은행제로 학위를 취득한 학생은 전문대학, 4년제 대학교 졸업생과 동등한 자격으로 일반편입 및 학사편입과 대학원 진학을 할 수 있습니다.

2. 전형유형

| 전형유형 | 지원자격 |

| 기초전형 |

인문, 자연, 예체능 계열 구분 없이 지원 가능 |

| 고급전형 |

전공자 지원 가능 전공계열 : 전자공학, 전기공학, 컴퓨터공학, 메카트로닉스학, 정보통신공학, 재료공학, 기계공학, 임베디드시스템공학, 반도체공학 |

1. 원격수업

2. 실습수업

본교육원은 수업 및 자격증 취득을 통해 교육부장관 명의의 '전문학사' 및 '학사학위' 취득이 가능하며 학점은행제로 학위를 취득한 학생은 전문대학, 4년제 대학교 졸업생과 동등한 자격으로 일반편입 및 학사편입과 대학원 진학을 할 수 있습니다.

| 번호 | 수업 내용 | 비고 |

| 1(이론 / 실습) |

- Inverter cross section/Inverter mask set

- CMOS schematic/CMOS stick diagram

- logic gate simulation의 이해(Transistor level) - IC-Chip Design Flow & IC Design Environment - Virtuoso 기본 기능 이해와 Setup

- 새로운 프로젝트 생성 및 계층도면의 이해

- Inverter Schematic, Symbol, Simulation

|

|

| 2(이론 / 실습) |

Cadence Schematic, Spectre Editor 실습

- Digatal logic gate library 구성

- Logic gate 회로 설계

- 2NAND, 3NAND, 2NOR, 3NOR schematic & simulation(Simulation option의 설정, Transient 해석/ Bias Point 해석, DC 해석)

|

|

| 3(실습) |

Cadence Virtuoso Layout Editor 설정 및 실습

- nMOS, pMOS layout - Inverter layout, DRC, LVS

- CMOS Inverter Layout & Assura DRC / LVS 검증 - GPDK090(DRM file)을 통한 Design Rule의 이해와 적용

VSE 단축키 및 사용방법 & Symbol 생성

ADE 환경설정 및 사용방법/VLD 단축키 및 사용방법

DRC, LVS 검증 방법/Inverter 회로를 기반으로 한 Flow 실습

|

|

| 4(실습) |

Cadence Virtuoso Layout Editor 설정 및 실습

- Digatal logic gate library 구성

2NAND, 3NAND, 2NOR, 3NOR Layout - Switch Layout - Assura DRC / LVS 검증 - 논리게이트 최소 사이즈 설계

|

|

| 5(실습) |

Cadence Schematic, Spectre Editor 실습

Cadence Virtuoso Layout Editor 실습

- 4NAND, 4NOR

Schematic, Simulation, Layout, DRC, LVS

- 2×1 Multiplexer 설계 1(Logic gate) Logic gate와 Switch 설계 비교

|

|

| 6(실습) |

Cadence Schematic, Spectre Editor 실습

Cadence Virtuoso Layout Editor 실습

- 4NAND, 4NOR

Schematic, Simulation, Layout, DRC, LVS

- 2×1 Multiplexer 설계 1(Logic gate) Logic gate와 Switch 설계 비교

|

|

| 7(실습) |

Cadence Virtuoso Layout Editor 실습

- 4×1 Multiplexer 설계 2

Logic gate와 Switch 설계 비교 - 4×1 Multiplexer Schematic, Simulation, Layout, DRC, LVS 검증

- Term project 1

|

|

| 8(실습) |

Cadence Virtuoso Layout Editor 실습

Cadence Virtuoso Layout Editor 실습

- Half Adder 설계 1

Schematic, Simulation, Layout, DRC, LVS 검증

|

|

| 9(실습) |

Cadence Schematic, Spectre Editor 실습

Cadence Virtuoso Layout Editor 실습

- XOR gate 설계

Schematic, Simulation, Layout, DRC, LVS 검증

- Full Adder 설계

Schematic, Simulation, Layout, DRC, LVS 검증

|

|

| 10(실습) |

Cadence Schematic, Spectre Editor실습

Cadence Virtuoso Layout Editor 실습

- 4bit Adder 설계

Schematic, Simulation, Layout, DRC, LVS 검증

- 4bit Adder/Substracter 설계 1

Schematic, Simulation, Layout, DRC, LVS 검증

|

|

| 11(실습) |

4bit Adder/Substracter 설계 2

Schematic, Simulation, Layout, DRC, LVS 검증

- Term project 2 - Presentation

|

|

1. 인터넷 원서접수

- 접수 가능일: 입시기간 중 모든 일정에 관계 없이 접 수 가능

- 접수 가능 시간: 24시간 인터넷 원서접수 가능

2. 오프라인 면접

- 면접은 지원자의 의지와 적성을 알아보는 것으로 기초상식에 관한 간략한 면접입니다.

- 면접 당일 신분증을 가지고 오시면 됩니다.

- 입학원서는 방문시 출력해드립니다.

3. 합격자 발표

- 합격자발표는 지정된 합격자 발표일에 홈페이지에서 확인 가능

- 합격자에게 SMS로 확인 문자를 보내드립니다.

1. 신입생 모집요강

본교육원은 수업 및 자격증 취득을 통해 교육부장관 명의의 '전문학사' 및 '학사학위' 취득이 가능하며 학점은행제로 학위를 취득한 학생은 전문대학, 4년제 대학교 졸업생과 동등한 자격으로 일반편입 및 학사편입과 대학원 진학을 할 수 있습니다.

2. 전형유형

| 전형유형 | 지원자격 |

| 기초전형 |

인문, 자연, 예체능 계열 구분 없이 지원 가능 |

| 고급전형 |

전공자 지원 가능 전공계열 : 전자공학, 전기공학, 컴퓨터공학, 메카트로닉스학, 정보통신공학, 재료공학, 기계공학, 임베디드시스템공학, 반도체공학 |

1. 원격수업

2. 실습수업

본교육원은 수업 및 자격증 취득을 통해 교육부장관 명의의 '전문학사' 및 '학사학위' 취득이 가능하며 학점은행제로 학위를 취득한 학생은 전문대학, 4년제 대학교 졸업생과 동등한 자격으로 일반편입 및 학사편입과 대학원 진학을 할 수 있습니다.

| 번호 | 수업 내용 | 비고 |

| 1(이론 / 실습) |

- Inverter cross section/Inverter mask set

- CMOS schematic/CMOS stick diagram

- logic gate simulation의 이해(Transistor level) - IC-Chip Design Flow & IC Design Environment - Virtuoso 기본 기능 이해와 Setup

- 새로운 프로젝트 생성 및 계층도면의 이해

- Inverter Schematic, Symbol, Simulation

|

|

| 2(이론 / 실습) |

Cadence Schematic, Spectre Editor 실습

- Digatal logic gate library 구성

- Logic gate 회로 설계

- 2NAND, 3NAND, 2NOR, 3NOR schematic & simulation(Simulation option의 설정, Transient 해석/ Bias Point 해석, DC 해석)

|

|

| 3(실습) |

Cadence Virtuoso Layout Editor 설정 및 실습

- nMOS, pMOS layout - Inverter layout, DRC, LVS

- CMOS Inverter Layout & Assura DRC / LVS 검증 - GPDK090(DRM file)을 통한 Design Rule의 이해와 적용

VSE 단축키 및 사용방법 & Symbol 생성

ADE 환경설정 및 사용방법/VLD 단축키 및 사용방법

DRC, LVS 검증 방법/Inverter 회로를 기반으로 한 Flow 실습

|

|

| 4(실습) |

Cadence Virtuoso Layout Editor 설정 및 실습

- Digatal logic gate library 구성

2NAND, 3NAND, 2NOR, 3NOR Layout - Switch Layout - Assura DRC / LVS 검증 - 논리게이트 최소 사이즈 설계

|

|

| 5(실습) |

Cadence Schematic, Spectre Editor 실습

Cadence Virtuoso Layout Editor 실습

- 4NAND, 4NOR

Schematic, Simulation, Layout, DRC, LVS

- 2×1 Multiplexer 설계 1(Logic gate) Logic gate와 Switch 설계 비교

|

|

| 6(실습) |

Cadence Schematic, Spectre Editor 실습

Cadence Virtuoso Layout Editor 실습

- 4NAND, 4NOR

Schematic, Simulation, Layout, DRC, LVS

- 2×1 Multiplexer 설계 1(Logic gate) Logic gate와 Switch 설계 비교

|

|

| 7(실습) |

Cadence Virtuoso Layout Editor 실습

- 4×1 Multiplexer 설계 2

Logic gate와 Switch 설계 비교 - 4×1 Multiplexer Schematic, Simulation, Layout, DRC, LVS 검증

- Term project 1

|

|

| 8(실습) |

Cadence Virtuoso Layout Editor 실습

Cadence Virtuoso Layout Editor 실습

- Half Adder 설계 1

Schematic, Simulation, Layout, DRC, LVS 검증

|

|

| 9(실습) |

Cadence Schematic, Spectre Editor 실습

Cadence Virtuoso Layout Editor 실습

- XOR gate 설계

Schematic, Simulation, Layout, DRC, LVS 검증

- Full Adder 설계

Schematic, Simulation, Layout, DRC, LVS 검증

|

|

| 10(실습) |

Cadence Schematic, Spectre Editor실습

Cadence Virtuoso Layout Editor 실습

- 4bit Adder 설계

Schematic, Simulation, Layout, DRC, LVS 검증

- 4bit Adder/Substracter 설계 1

Schematic, Simulation, Layout, DRC, LVS 검증

|

|

| 11(실습) |

4bit Adder/Substracter 설계 2

Schematic, Simulation, Layout, DRC, LVS 검증

- Term project 2 - Presentation

|

|

1. 인터넷 원서접수

- 접수 가능일: 입시기간 중 모든 일정에 관계 없이 접 수 가능

- 접수 가능 시간: 24시간 인터넷 원서접수 가능

2. 오프라인 면접

- 면접은 지원자의 의지와 적성을 알아보는 것으로 기초상식에 관한 간략한 면접입니다.

- 면접 당일 신분증을 가지고 오시면 됩니다.

- 입학원서는 방문시 출력해드립니다.

3. 합격자 발표

- 합격자발표는 지정된 합격자 발표일에 홈페이지에서 확인 가능

- 합격자에게 SMS로 확인 문자를 보내드립니다.

|

|